企业免费推广平台

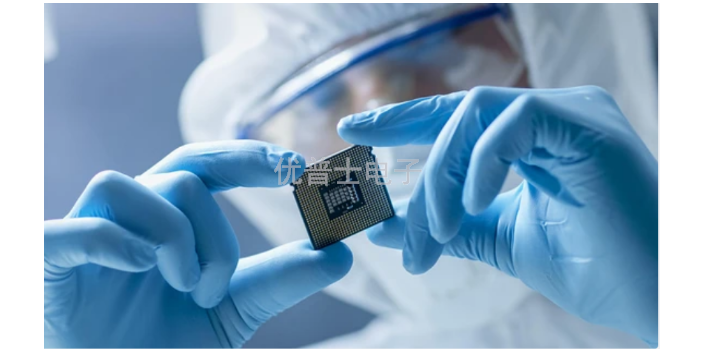

MCU(Micro Control Unit)芯片称为微控制单元,又称作单片机,是许多控制电路中的重要组成部分.MCU芯片的设计和制造的发展要依赖于芯片的测试,随着芯片可测试管脚数量的增多,芯片的功能也随之增多,芯片测试的复杂度和测试时间也随之增加,深圳自动化芯片测试.芯片测试系统从1965年至今已经历了四个阶段,目前的芯片测试系统无论在测试速度还是在可测试管脚数量方面都比以前有了很大提升,深圳自动化芯片测试,但是任何一个芯片测试系统也无法完全满足由于不断更新的芯片而引起的对测试任务不断更新的要求.设计安全性高,深圳自动化芯片测试,测试效率高,系统升级成本低的芯片测试系统是发展的方向。 优普士电子为半导体后段整合服务厂商!深圳自动化芯片测试

一般是从测试的对象上分为WAT、CP、FT三个阶段,WAT: Wafer Acceptance Test,是晶圆出厂前对testkey的测试。采用标准制程制作的晶圆,在芯片之间的划片道上会放上预先一些特殊的用于专门测试的图形叫testkey。CP:Circuit Probe,是封装前晶圆级别对芯片测试。这里就涉及到测试芯片的基本功能了。不同项目的失效,会分别以不同颜色表示出来。失效的项目反映的是芯片设计的问题。FT:Final test,封装完成后的测试,也是接近实际使用情况的测试,会测到比CP更多的项目,处理器的不同频率也是在这里分出来的。这里的失效反应封装工艺上产生的问题,比如芯片打线不好导致的开短路。深圳Flash芯片测试是什么意思拥有良好的作业环境,ISO管理模式,各种先进的烧录测试设备。

芯片测试在什么环节进行?现在芯片面积越来越大,测试相当具有挑战性。所以如何测试其实是一门很深的学问。由于信号过多,不可能把每个信号都引出来测试,所以肯定在设计的时候就要做可测性实际,就是DFT。DFT简而言之,DFT就是通过某种方法间接观察内部信号的情况,例如scanchain之类。然后通过特定的测试仪器来测试——这种仪器不是简单的示波器,它要能产生各种测试波形并检测输出,所以一套平台大概要上百万。而且这些DFT比较适合于小芯片,大芯片像CPU之类的还会使用内建自测试(built-inselftest),让芯片自己在上电后可以执行测试,这样就大大减小了测试人员的工作量。DFT测试通过之后,就到正式的芯片测试环节了。

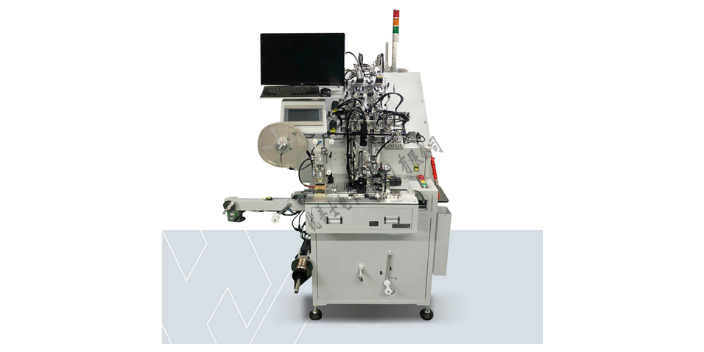

芯片分选机 1)集成电路封装形式的多样性要求分选机具备对不同封装形式集成电路进行测试时能够快速切换的能力,从而形成较强的柔性化生产能力及适应性;2)由于集成电路的小型化和集成化特征,分选机对自动化高速重复定位控制能力和测压精度要求较高,误差精度普遍要求在0.01mm等级;3)分选机的批量自动化作业要求其具备较强的运行稳定性,例如对UPH(每小时运送集成电路数量)和JamRate(故障停机比率)的要求很高;4)集成电路测试对外部测试环境有一定要求,例如部分集成电路测试要求在-55—150℃的多种温度测试环境、无磁场干扰测试环境、多种外场叠加的测试环境中进行,如何给定相应的测试环境是分选机技术难点。提供专业芯片测试+烧录服务。

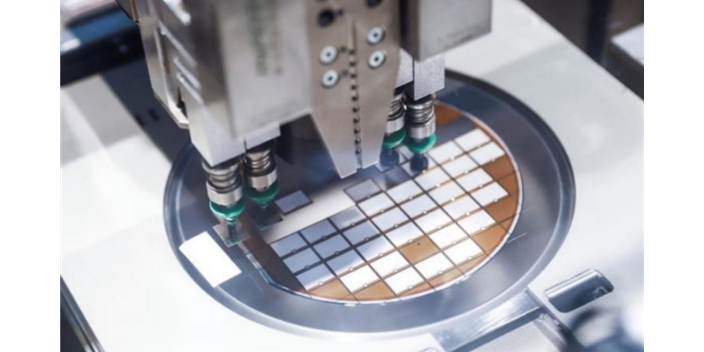

探针台 1)晶圆检测需具备多套视觉精密测量及定位系统,并具备视觉相互标定、多个坐标系互相拟合的功能;2)探针台精度要求非常严苛,重复定位精度要求达到0.001mm(微米)等级;3)探针台对设备工作环境洁净度要求较高,除需达到几乎无人干预的全自动化作业,对传动机构低粉尘提出要求,还需具备气流除尘等特殊功能。4)晶圆检测对于设备稳定性要求较高,各个执行器件均需进行多余度的控制,晶圆损伤率要求控制在1ppm(百万分之一)以内;芯片测试是必不可少的工段。深圳量产芯片测试口碑推荐

OPS助力中国芯科技之发展,赋能于半导体产业的专业化测试、烧录服务。深圳自动化芯片测试

FT:Finaltest,封装完成后的测试,也是接近实际使用情况的测试,会测到比CP更多的项目,处理器的不同频率也是在这里分出来的。这里的失效反应封装工艺上产生的问题,比如芯片打线不好导致的开短路。FT是工厂的重点,需要大量的机械和自动化设备。它的目的是把芯片严格分类。以Intel的处理器来举例,在FinalTest中可能出现这些现象:虽然通过了WAT,但是芯片仍然是坏的。封装损坏。芯片部分损坏。比如CPU有2个主件损坏,或者GPU损坏,或者显示接口损坏等。芯片是好的,没有故障。深圳自动化芯片测试

本站提醒: 以上信息由用户在商名网发布,信息的真实性请自行辨别。服务协议 - 信息投诉/删除/联系本站

优普士电子(深圳)有限公司 Copyright © 商名网营销建站平台 All Rights Reserved.